### **COM Express® Mini Module**

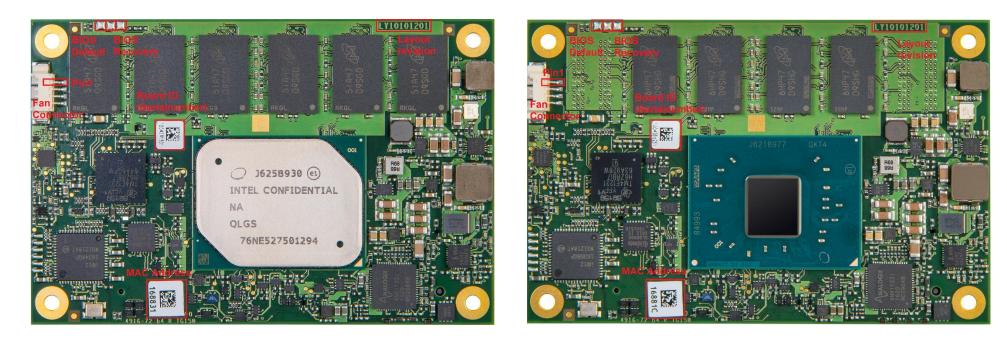

MSC C10M-AL

### **Type 10 Pinout**

Intel<sup>®</sup> Atom<sup>™</sup> / Celeron<sup>®</sup> / Pentium<sup>®</sup> Series SOC

Rev. 1.1 2022-05-17

### Preface

### **Copyright Notice**

Copyright © 2022 Avnet Embedded GmbH. All rights reserved.

Copying of this document and providing to others and the use or communication of the contents thereof is forbidden without express authority of Avnet Embedded GmbH. Offenders are liable to the payment of damages.

All rights are reserved in the event of the grant of a patent or the registration of a utility model or design.

#### **Important Information**

This documentation is intended for qualified audiences only. The product described herein is not an end user product. It was developed and manufactured for further processing by trained personnel.

#### Disclaimer

Although this document has been generated with the utmost care no warranty or liability for correctness or suitability for any particular purpose is implied. The information in this document is provided "as is" and is subject to change without notice.

### **EMC** Rules

This unit must be installed in a shielded housing. If not installed in a properly shielded enclosure, and used in

accordance with the instruction manual, this product may cause radio interference in which case the user may be required to take adequate measures at his or her owns expense.

### Trademarks

All used product names, logos or trademarks are property of their respective owners.

### Certification

Avnet Embedded GmbH is certified according to DIN EN ISO 9001:2015 standards.

### Life-Cycle-Management

Avnet Embedded /MSC products are developed and manufactured according to high quality standards. Our lifecycle management assures long term availability through permanent product maintenance. Technically necessary changes and improvements are introduced if applicable. A product-change-notification and end-of-life management process assures early information of our customers.

### **Product Support**

Avnet Embedded /MSC engineers and technicians are committed to provide support to our customers whenever needed.

Before contacting Avnet Embedded /MSC Technical Support, please consult the respective pages on our web site at <u>embedded.avnet.com</u> for the latest documentation, drivers and software downloads.

If the information provided there does not solve your problem, please contact us in Avnet Embedded /MSC Technical Support:

Phone: +49 8165 906-200

E-Mail: <u>support.boards@avnet.eu</u>

### Contents

| 1    | USER           | INFORMATION                               | 8  |

|------|----------------|-------------------------------------------|----|

| 1.1  |                | ut this Manual                            |    |

| 1.2  |                | bols and Signal Words                     |    |

| 1.3  |                | le Cells with Gray Text                   |    |

| 1.4  |                | nded Use                                  |    |

| 1.5  |                | -intended use                             |    |

| 1.6  |                | trostatic Sensitive Device                |    |

|      |                |                                           |    |

| 2    |                | NICAL DESCRIPTION                         |    |

| 2.1  |                | oduction                                  |    |

| 2.2  |                | Features                                  |    |

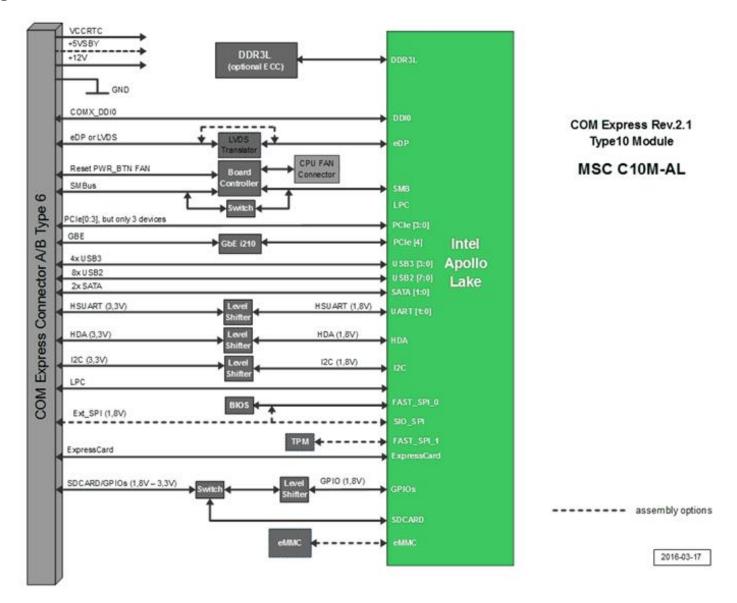

| 2.3  | Bloo           | k Diagram                                 | 12 |

| 2.4  | CON            | I Express Implementation                  | 13 |

| 2.5  | Fun            | ctional Units                             | 15 |

| 2.6  | Pow            | er Supply                                 | 17 |

| 2.7  | Pow            | ver Dissipation                           | 17 |

| 2.   | 7.1            | Running Mode                              | 17 |

| 2.   | 7.2            | Power Dissipation (Standby Modes)         | 18 |

| 2.8  | Sys            | tem Memory                                | 19 |

| 2.9  | eMN            | IC                                        | 19 |

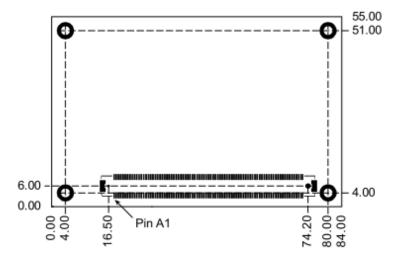

| 2.10 | Mec            | hanical Dimensions                        | 20 |

| 2.   | 10.1           | Mini Module                               | 20 |

| 2.11 | The            | rmal Specifications                       | 21 |

| 2.12 |                | Conditions                                |    |

| 2.13 |                | nal Description                           |    |

| 2.   | 13.1           | High Definition Audio                     | 23 |

| 2.   | 13.2           | Ethernet                                  | 23 |

| 2.   | 13.3           | Serial ATA                                | 24 |

| 2.   | 13.4           | PCI Express Lanes                         |    |

| 2.   | 13.5           | Express Card Support                      |    |

|      | 13.6           | USB                                       |    |

|      | 13.7           | LPC Bus                                   | -  |

|      | 13.8           | LVDS/eDP                                  | -  |

|      | 13.9           | Digital Display Interfaces                | 31 |

|      | 13.10<br>13.11 | Serial Interface Signals<br>Miscellaneous |    |

|      | 13.11          | Power and System Management               |    |

|      | 13.12          | General Purpose I/O                       |    |

|      | 13.13          | SDIO                                      |    |

| 4.   |                |                                           | 00 |

| 2.13.15<br>2.13.16<br>2.13.17<br>2.14 Pin | SPI Interface<br>Module Type Definition<br>Power and GND<br>List | . 38<br>. 38 |

|-------------------------------------------|------------------------------------------------------------------|--------------|

| 3.1 Jun                                   | PERS AND CONNECTORS                                              | .44          |

| 4 WATC                                    | CHDOG                                                            | 45           |

|                                           | EM RESOURCES<br>3 Address Map                                    |              |

| 6 BIOS                                    |                                                                  | 48           |

| 6.1 Intro                                 | oduction                                                         | . 48         |

| 6.2 Star                                  | tup Screen Overview                                              | .48          |

| 6.3 Acti                                  | vity Detection Background                                        | .48          |

| 6.4 Apt                                   | io Setup Utility                                                 | .48          |

| 6.5 Con                                   | figuring the System BIOS                                         | .48          |

| 6.6 BIO                                   | S Menu Structure                                                 | 48           |

| 6.6.1                                     | Menu Bar                                                         |              |

| 6.6.2                                     | Legend Bar                                                       |              |

| 6.7 Mai                                   | n Menu                                                           |              |

| 6.7.1                                     | Board Info                                                       | -            |

| 6.7.2                                     | Hardware Monitoring                                              |              |

| 6.7.3                                     | System Information                                               |              |

| 6.7.4                                     | Firmware Update                                                  |              |

| 6.7.5                                     | Network Configuration                                            | . 56         |

| 6.8 Adv                                   | anced Menu                                                       | . 58         |

| 6.8.1                                     | Trusted Computing (TPM)                                          | . 59         |

| 6.8.2                                     | ACPI Settings                                                    | . 59         |

| 6.8.3                                     | SMART Settings                                                   |              |

| 6.8.4                                     | Serial Port Console Redirection                                  | . 60         |

| 6.8.5                                     | Console Redirection Submenu                                      |              |

| 6.8.6                                     | CPU Configuration                                                |              |

| 6.8.7                                     | CPU Power Management Submenu                                     |              |

| 6.8.8                                     | AMI Graphic Output Protocol Policy                               |              |

| 6.8.9                                     | PCI Subsystem                                                    |              |

| 6.8.10                                    | Network Stack Configuration                                      |              |

| 6.8.11                                    | CSM Configuration                                                | . 66         |

| 6.8.12   | NVMe Configuration                        | 67 |

|----------|-------------------------------------------|----|

| 6.8.13   | SDIO Configuration                        |    |

| 6.8.14   | USB Configuration                         |    |

| 6.8.15   | Security Configuration                    |    |

|          |                                           |    |

| 6.8.16   | SIO WB627/ SMSC 3114 Configuration        |    |

| 6.8.17   | EC Hardware Monitoring                    |    |

| 6.8.18   | EC Features Configuration                 | 77 |

| 6.8.19   | Module-specific Initialization            | 78 |

| 6.8.20   | Onboard GPIO configuration                | 79 |

| 6.8.21   | System Component                          | 79 |

| 6.9 Chij | pset                                      | 80 |

| 6.9.1    | Flat Panel Configuration                  | 80 |

| 6.9.2    | Backlight Control                         | 81 |

| 6.9.3    | North Bridge                              | 82 |

| 6.9.4    | South Bridge                              | 82 |

| 6.9.5    | Uncore Configuration                      | 83 |

| 6.9.6    | South Cluster Configuration               | 84 |

| 6.9.7    | HD Audio Configuration                    | 85 |

| 6.9.8    | LPSS Configuration                        | 85 |

| 6.9.9    | PCI Express Configuration                 | 86 |

| 6.9.10   | PCIE Express Root Port A 0-3 and B1 (LAN) | 87 |

| 6.9.11   | SATA Drives                               |    |

| 6.9.12   | SCC Configuration                         | 89 |

| 6.9.13   | USB Configuration                         | 90 |

| 6.9.14   | Miscellaneous Configuration               |    |

|          |                                           |    |

| 6.10<br>6.10<br>6.11<br>6.12<br>6.13<br>6.14<br>6.15<br>6.16<br>6.17 |                                                          | 92<br>93<br>93<br>96<br>98<br> |

|----------------------------------------------------------------------|----------------------------------------------------------|--------------------------------|

| 6.18<br>6.19<br>6.20<br>6.21                                         | Bios Recovery<br>Trusted Update<br>Jumpers<br>Post Codes | 105<br>109                     |

| 8 E                                                                  | ECHNOTES<br>API<br>ROUBLESHOOTING                        | 112                            |

# **INDET** EMBEDDED

### **Revision History**

| Rev. | Date       | Description                                                    |

|------|------------|----------------------------------------------------------------|

| 1.0  | 2021-03-08 | First Release                                                  |

| 1.1  | 2022-05-17 | Added USB Overcurrent connection info. Adapted Corporate info. |

|      |            |                                                                |

|      |            |                                                                |

|      |            |                                                                |

|      |            |                                                                |

# **VNET**<sup>°</sup>EMBEDDED

### **Reference Documents**

- [1] COM Express Module Base Specification COM Express Revision 2.1 Last update: April 10<sup>th</sup>, 2012

- [2] PCI Local Bus Specification Rev. 2.1 PCI21.PDF Last update: June 1<sup>st</sup>, 1995 <u>http://www.pcisig.com</u>

- [3] ATA/ATAPI-6 Specification d1410r3b.pdf <u>http://www.t13.org/</u>

- [4] Serial ATA Specification Serial ATA 1.0 gold.pdf Last update: August 29<sup>th</sup>, 2002 Rev.1.0 <u>http://www.sata-io.org/</u>

- [5] IEEE Std. 802.3-2002 802.3-2002.pdf http://www.ieee.org

- [6] VESA Embedded DisplayPort Standard

- eDP\_v1\_3 mem.pdf

Last update: 13.01.2012

http://www.vesa.org/

- [7] Universal Bus Specification usb\_20.pdf Last update: April 27<sup>th</sup>, 2000 http://www.usb.org

- [8] Universal Serial Bus Revision 3.0 Specification usb\_30\_spec\_xxxxx.zip Last update: 13.08.2012 <u>http://www.usb.org</u>

### **1** User Information

### **1.1** About this Manual

This user's guide provides information about the components, features and connectors available on the MSC C10M-AL COM Express® Mini Module.

#### 1.2 Symbols and Signal Words

Safety Messages: Danger, Warning and Caution No safety messages used in this manual, due to high compact module security. The following paragraph shows the usual MSC standard.

Signal words call attention to a safety message and designate a degree or level of hazard seriousness.

| Signal word | Degree of hazard seriousness                                                                    |

|-------------|-------------------------------------------------------------------------------------------------|

| Danger      | Indicates a hazardous situation that, if not avoided, will result in death or serious injury.   |

| Warning     | Indicates a hazardous situation that, if not avoided, could result in death or serious injury.  |

| Caution     | Indicates a hazardous situation that, if not avoided, could result in minor or moderate injury. |

### 1.4 Intended Use

High-performance embedded modules can perform various tasks in infotainment systems, such as professional audio equipment for radio and television, or sophisticated illumination engineering for theater

All safety messages have a safety alert symbol and are structured as follows:

Danger, Warning or Caution

Type of hazard

Potential consequences of the hazard

Evasive or avoidance actions to be taken

#### Notice

Notices contain important information that should be observed. In case of neglect the board can be damaged. All notices have the ①-symbol and are structured as follows:

(i) NOTICE: Notice text.

### 1.3 Table Cells with Gray Text

Cells with gray text contain information that is not supported on this board.

performances. The MSC C10M-AL module is based on Intel's multicore system-on-chip (SOC) Atom generation that integrates next generation Intel processor core, graphics, memory, and I/O interfaces into one solution. Do not use this Mini Module in any other circumstances, as described herein.

### 1.5 Non-intended use

(i) NOTICE: Use the compact module in the specified temperature ranges only!

1 NOTICE: Use the compact module in the specified humidity ranges only!

**(i)** NOTICE: Handle the Compact Module at electrostatic-free workstations only.

(i) NOTICE: Do not handle or store the Compact Module near strong electrostatic, electromagnetic, magnetic or radioactive fields unless the Compact Module is contained within its original packaging

### **1.6 Electrostatic Sensitive Device**

The MSC COM Express® Mini Module is an electrostatic sensitive device. It is packed accordingly.

### 2 **Technical Description**

### 2.1 Introduction

COM Express® is an open specification from PICMG (PCI Industrial Computer Manufacturer Group). It is a module concept to bring PCI Express and other newer technologies like SATA, USB 3.0 and different display interfaces onto a COM (Computer On Module).

A COM Express® module is plugged onto an application-specific base board and offers a migration path to future CPU technologies as they become available. Utilizing different form factors, COM Express® can be used for deeply embedded solutions all the way up to high performance platforms.

The design of the MSC C10M-AL module supports the Intel® Atom-Series System-on-Chip (SOC) platform enabling the embedded application to provide high performance processing with an excellent visual experience, together with power efficiency.

For evaluation and design-in of the COM Express® modules MSC offers evaluation baseboards and development motherboards providing the interface infrastructure for the COM Express® module using PC type connectors for external access.

Currently four module sizes are defined in the COM Express® Specification 2.1: the Mini Module, the Compact Module, the Basic Module and the Extended Module. The main difference between them is the over-all physical size and the performance envelope supported.

All module sizes of the same type use the same connectors and pinouts and utilize several common mounting hole positions. This level of compatibility permits a carrier board designed to accommodate an Extended Module to also support a Basic or Compact Module.

Up to 440 pins of connectivity are available between COM Express® modules and the Carrier Board. Legacy buses such as PCI, parallel ATA, LPC, HDA are supported as well as new high speed serial interconnects such as PCI Express, Serial ATA and Gigabit Ethernet.

To enhance interoperability between COM Express® modules and Carrier Boards, seven common signaling configurations (Pin-out Types) have been defined to ease system integration.

### 2.2 Key Features

The MSC C10M-AL COM Express® module is designed as a type 10 module according to COM Express® Module Base Specification Revision 2.1.

Key features include:

- Module size: 84 mm x 55 mm

- Intel<sup>®</sup> Atom<sup>™</sup> / Celeron<sup>®</sup> / Pentium<sup>®</sup> Series System-on-Chip (SOC)

- Single 220 pin connector

- DDR3L on module up to 8 GB (optional ECC)

- Up to eight USB 2.0 ports; two can be used as USB 3.0 port; 4 shared over-current lines

- Two Serial ATA 6.0 Gbit/s ports

- Four PCI Express lanes for three devices

- Support pins for two Express Cards

- Display interfaces

- two independent display controllers

- Digital Display Interface (DDI) configurable as HDMI, DVI or Display Port

- Single channel 24-bit LVDS channel (shared with eDP mounting option)

- High definition digital audio interface (external CODEC)

- Single GBit Ethernet interface (Intel® Ethernet Controller I210-AT or I210-IT)

- LPC interface

- Two high speed UART ports (TX and RX only, 16550 compliant)

- BIOS support for Super IO Winbond 83627 (on carrier board via LPC interface)

- Four GPI pins

- Four GPO pins

- +12V primary power supply input

- +5V standby (optional) and 3.3V RTC power supply inputs

- TPM module (optional TPM 2.0, SLB9670)

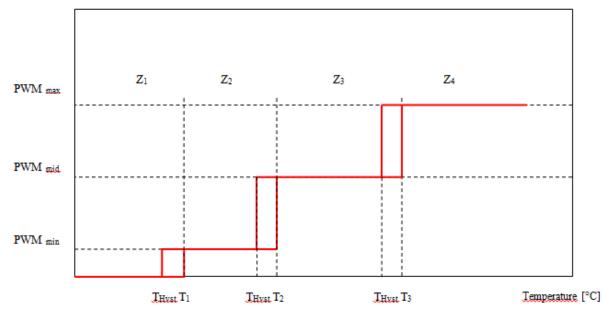

- Automatic fan control

- Watchdog timer

- Optional eMMC<sup>TM</sup> memory on module

#### 2.3 Block Diagram

### 2.4 COM Express Implementation

COM Express® required and optional features for pin-out type 10 are summarized in the following table. The features identified as Minimum (Min.) **shall** be implemented by all modules. Features identified up to Maximum (Max) **may** be additionally implemented by a module.

|     |                         | Type 10   | MSC C10M-AL | Note                                                                              |

|-----|-------------------------|-----------|-------------|-----------------------------------------------------------------------------------|

|     |                         | Min / Max |             |                                                                                   |

|     | System I/O              |           |             |                                                                                   |

| A-B | PCI Express Lanes 0 - 3 | 1 / 4     | 4 (x1)      | For three devices.                                                                |

| A-B | LVDS Channels           | 0 / 1     | 1           | 1x single channel, 1x24 Bit, Only available on modules with LVDS mounting option. |

| A-B | eDP on LVDS CH A pins   | 0 / 1     | 1           | Only available on modules with eDP mounting option.                               |

| A-B | VGA Port                | NA        | 0           |                                                                                   |

| A-B | TV-Out                  | NA        | 0           |                                                                                   |

| A-B | DDI 0                   | 0 / 1     | 1           |                                                                                   |

| A-B | Serial Ports 1-2        | 0 / 2     | 2           | HSUART                                                                            |

| A-B | CAN interface on SER1   | 0 / 1     | 0           |                                                                                   |

| A-B | SATA Ports              | 1 / 2     | 2           | SATA 6.0 GBit/s                                                                   |

| A-B | HDA Digital Interface   | 0 / 1     | 1           |                                                                                   |

| A-B | USB 2.0 Ports           | 4 / 8     | 8           |                                                                                   |

| A-B | USB Client              | 0 / 1     | 1           | USB Port 7                                                                        |

| A-B | USB 3.0 Ports           | 0 / 2     | 2           |                                                                                   |

| A-B | LAN Port 0              | 1 / 1     | 1           | Intel® Ethernet Controller I210-AT or Intel® Ethernet Controller I210-IT          |

| A-B | Express Card Support    | 1 / 2     | 1           |                                                                                   |

| A-B | LPC Bus                 | 1 / 1     | 1           |                                                                                   |

| A-B | SPI                     | 1 / 2     | 1           |                                                                                   |

|     | System Management       |           |             |                                                                                   |

| A-B | SDIO (muxed on GPIO)    | 0 / 1     |             | Max. UHS-I                                                                        |

|     | General Purpose Inputs  | 4 / 4     | 4           |                                                                                   |

| _   | General Purpose Outputs | 4 / 4     | 4           |                                                                                   |

|     | SMBus                   | 1 / 1     | 1           |                                                                                   |

| A-B | l <sup>2</sup> C        | 1 / 1     | 1           |                                                                                   |

| A-B | Watchdog Timer          | 0 / 1     | 1           |                                                                                   |

The column MSC C10M-AL shows the features implemented by the MSC module.

| \-Β | B Speaker Out               | 1/1   | 1 |                         |                         |

|-----|-----------------------------|-------|---|-------------------------|-------------------------|

| A-B | B External BIOS ROM support | 0/2   | 1 |                         |                         |

| A-B | B Reset Functions           | 1 / 1 | 1 |                         |                         |

|     |                             |       |   |                         |                         |

|     | Power Management            |       |   |                         |                         |

| A-B | 3 Thermal Protection        | 0 / 1 | 0 |                         |                         |

| A-B | Battery Low Alarm           | 0 / 1 | 1 |                         |                         |

| A-B | 3 Suspend                   | 0 / 1 | 1 |                         |                         |

| A-B | 3 Wake                      | 0 / 2 | 2 |                         |                         |

|     | Power Button Support        | 1 / 1 | 1 |                         |                         |

| A-B | Power Good                  | 1 / 1 | 1 |                         |                         |

| A-B | VCC_5V_SBY Contacts         | 4 / 4 | 4 |                         |                         |

| A-B | 3 Sleep Input               | 0 / 1 | 1 |                         |                         |

| A-B | Lid Input                   | 0 / 1 | 1 |                         |                         |

|     | Fan Control Signals         | 0 / 2 | 2 |                         |                         |

| A-B | 3 Trusted Platform Modules  | 0 / 1 | 1 | optional TPM 2.0 module | optional TPM 2.0 module |

### 2.5 Functional Units

CPUs Intel® Atom<sup>TM</sup> x5-E3930, DC, 1.30GHz, 1.80GHz Burst, 2 MB L2 Cache, 6.5W, 2ch DDR3L. (APL-I) (FCBGA 1296 package) Intel® Atom<sup>TM</sup> x5-E3940, QC, 1.60GHz, 1.80GHz Burst, 2 MB L2 Cache, 9.5W, 2ch DDR3L. (APL-I) Intel® Atom<sup>TM</sup> x7-E3950, QC, 1.60GHz, 2.00GHz Burst, 2 MB L2 Cache, 12W, 2ch DDR3L. (APL-I) Intel® Pentium<sup>TM</sup> N4200, QC, 1.10GHz, 2.50GHz Burst, 2 MB L2 Cache, 6W, 2ch DDR3L Intel® Celeron<sup>TM</sup> N3350, DC, 1.10GHz, 2.40GHz Burst, 2 MB L2 Cache, 6W, 2ch DDR3L. E3930, E3940, E3950: T<sub>JUNCTION</sub> = - 40°C to 110°C (APL-I, integrated heat spreader) N3350, N4200: T<sub>JUNCTION</sub> =0°C to 105°C

Memory DDR3L on module for up to 8GB non-ECC unbuffered. (optional: ECC at Atom<sup>™</sup> x CPUs and DDR3L-1600) PC3-12800 DDR3L SDRAM (DDR3L-1600), PC3-14900 DDR3L SDRAM (DDR3L-1866).

SATA 2 SATA channels up to 6.0 GBit/s

USB 8 x USB 2.0, 2 x USB 3.0/2.0

USB Client 1 x USB 2.0 client

COM Express® Type 10 interface, fully compliant to COM Express Base Specification R2.1

PCI Express<sup>™</sup> Four channels PCIe x1. (For three devices)

LPC Low Pin Count Bus for heritage interfaces

SPI Serial Peripheral Interface for one 1.8 V SPI flash device

Graphics Integrated Intel<sup>®</sup> HD Graphics 505 with Atom<sup>™</sup> x7 and Pentium<sup>®</sup> CPU

Controller Integrated Intel<sup>®</sup> HD Graphics 500 with Atom<sup>™</sup> x5 and Celeron<sup>®</sup> CPUs

LVDS Single channel 24-bit LVDS (Only available on modules with LVDS mounting option.)

Digital Display Two Digital Display Interfaces (DDI) (One is shared with LVDS) Ports DP (4096x2304@60Hz) HDMI (3840x2160@30Hz)

eDP (3840x2160@60Hz)

- Ethernet 10/100/1000Base-TX (Intel® Ethernet Controller I210-AT for commercial temperature or Intel® Ethernet Controller I210-IT for industrial temperature)

- Sound Interface High Definition Audio Interface

Serial Interface Two High Speed UARTs

Watchdog Timer Embedded controller creates watchdog alert and system reset

TPM (option) Optional TPM module, TPM 2.0, SLB9670

Fan Supply 4-pin header for support of a 12V PWM fan

Real Time Clock RTC integrated in Intel® Atom SOC

CMOS Battery External

System Monitoring Voltages, temperatures, fan

- Core voltage

- 3.3V onboard voltage

- 12V input voltage

- 5V SBY input voltage

- CPU temperature (0°C 100°C)

- System memory temperature

- Board temperature

- Fan speed and automatic fan speed control

- SSD Optional on module eMMC SSD

### 2.6 Power Supply

- +12V primary power supply input

- +5V standby

Option, is not required for module operation.

If not present, customer must ensure that the supply voltages which are generated on the carrier board are switched off during suspend states, so that no current from the carrier board's signal lines can flow to the CPU board.

#### 3.3V RTC power supply

Option, is not required for module operation.

BIOS SETUP data is stored in a nonvolatile backup memory device, therefore configuration data will not get lost after power removal (except for time and date information)

| 2.7 Power | Dissipation |

|-----------|-------------|

|-----------|-------------|

#### 2.7.1 Running Mode

All measurements were made by plugging the MSC C10M-AL module onto a MSC C10-MB-EVA carrier. The module was equipped with various memory quantities. The table below shows typical values which refer to consumption of the module itself without consumption of the base board and CPU fan.

| Voltage              | Input range     | Power Consumption    |  |  |

|----------------------|-----------------|----------------------|--|--|

| +12V                 | +4.75V - 20 V   | Defer to chapter 0.7 |  |  |

| +5V Standby          | +4.75V - 5.25 V | Refer to chapter 2.7 |  |  |

| +3V RTC power supply | +2.5V - 3.47V   | Тур. 4.3 μА          |  |  |

The following applications have been tested with minimum 15 minutes measurement time:

- Windows desktop (idle) under Microsoft Windows 10 64-bit.

- Running Intel<sup>®</sup> Thermal Analysis Tool (TAT!) Ver. 6.x to achieve TDP workload under Microsoft Windows 10 64-bit.

- BurnInTest V7.1 Pro with test settings 100% CPU, 100% RAM, 100% 2D Graphics and 100% 3D Graphics.

|                                                                                                                                |             | Win 10               | BurnInTest           |         |

|--------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|----------------------|---------|

| Module / CPU                                                                                                                   | Win 10 Idle | average              | peak                 | Dummest |

| C10M-AL-E3930-240201I (Intel <sup>®</sup> Atom <sup>™</sup> x5-E3930, 2C, 1.30GHz, 1.80GHz, 2MiB L2 Cache, 6.5W) 4GB non ECC   | 2.5 W       | 10.3 W               | 12.0 W               | 5.7 W   |

| C10M-AL-E3940- 240201I (Intel <sup>®</sup> Atom <sup>™</sup> x5- E3940, 4C, 1.60GHz, 1.80GHz, 2MiB L2 Cache, 9.5W) 4GB non ECC | 2.5 W       | 14.1 W               | 14.7 W               | 7.5 W   |

| C10M-AL-E3950- 351101I (Intel <sup>®</sup> Atom <sup>™</sup> x7-E3950, 4C, 1.60GHz, 2.00GHz, 2MiB L2 Cache, 12W) 8GB ECC       | 2.8 W       | 20.6 W               | 25.2 W               | 9.7 W   |

| C10M-AL-N4200- 350201C (Intel <sup>®</sup> Pentium <sup>™</sup> N4200, 4C, 1.10GHz, 2.50GHz, 2MiB L2 Cache, 6W) 8GB non ECC    | 2.6 W       | 10.0 W <sup>1)</sup> | 25.2 W <sup>1)</sup> | 10.2 W  |

<sup>1)</sup> TAT workload setting: CPU-All 100%, Gfx 80% in Intel<sup>®</sup> Thermal Analysis Tool Ver. 6.0.1030, because TAT do not offer TDP for this SKU.

#### 2.7.2 Power Dissipation (Standby Modes)

1. System is shut down into "Suspend to RAM" (S3) by Windows 10 64-bit with Wake on LAN enabled.

2. System is shut down into "Soft Off" (S5) or "Suspend to Disk" (S4) by Windows 10 64-bit with Wake on LAN enabled.

| Module / CPU                                                                                                                   | Input Power | <b>S</b> 3 | S4 / S5 |

|--------------------------------------------------------------------------------------------------------------------------------|-------------|------------|---------|

| C10M-AL-E3930-240201I (Intel <sup>®</sup> Atom <sup>™</sup> x5-E3930, 2C, 1.30GHz, 1.80GHz, 2MiB L2 Cache, 6.5W) 4GB non ECC   | 5V_SBY      | 0.45 W     | 0.32 W  |

| C10M-AL-E3940- 240201I (Intel <sup>®</sup> Atom <sup>™</sup> x5- E3940, 4C, 1.60GHz, 1.80GHz, 2MiB L2 Cache, 9.5W) 4GB non ECC | 5V_SBY      | 0.36 W     | 0.23 W  |

| C10M-AL-E3950- 351101I (Intel <sup>®</sup> Atom <sup>™</sup> x7-E3950, 4C, 1.60GHz, 2.00GHz, 2MiB L2 Cache, 12W) 8GB ECC       | 5V_SBY      | 0.52 W     | 0.33 W  |

| C10M-AL-N4200- 350201C (Intel <sup>®</sup> Pentium <sup>™</sup> N4200, 4C, 1.10GHz, 2.50GHz, 2MiB L2 Cache, 6W) 8GB non ECC    | 5V_SBY      | 0.59 W     | 0.29 W  |

### 2.8 System Memory

The MSC C10M-AL CPU module provides on board memory which have to meet the following demands:

- non-ECC DDR3L and ECC DDR3L

- 1.35V Supply Voltage

- DDR3L-1600 / PC3-12800, DDR3L-1866 / PC3-14900 (ECC DDR3L only with DDR3L-1600)

- SPD (Serial Presence Detect) EEPROM.

- At temperatures above +60°C the memory refresh rate must be doubled with BIOS option <u>DDR double Refresh Rate</u> set to Enabled.

### 2.9 eMMC

When using the on-module eMMC storage device, it should be taken into consideration that the lifetime of the device is affected by the number of read/write and erase cycles. It is not recommended to use eMMC storage devices with applications which are continually storing large amounts of data.

The eMMC device uses MLC (Multi Level Cell) technology.

| Temperature Grade           | Technology | Memory Size | Chip Identification        |

|-----------------------------|------------|-------------|----------------------------|

| Extended (-25°C to +85°C)   | MLC        | 16 GByte    | Micron MTFC16GAKAECN-2M WT |

|                             |            |             | SanDisk SDINBDG4-16G-I1    |

| Extended (-25°C to +85°C)   | MLC        | 32 GByte    | Micron MTFC32GAKAECN-3M WT |

|                             |            |             | SanDisk SDINBDG4-32G-I1    |

| Industrial (-40°C to +85°C) | MLC        | 16 GByte    | Micron MTFC16GAKAECN-4M IT |

|                             |            |             | SanDisk SDINBDG4-16G-XI1   |

| Industrial (-40°C to +85°C) | MLC        | 32 GByte    | Micron MTFC32GAKAECN-4M IT |

|                             |            |             | SanDisk SDINBDG4-32G-XI1   |

() NOTICE: With Windows 7 eMMC is not supported.

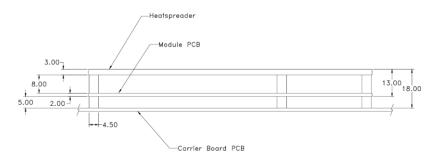

#### 2.10 Mechanical Dimensions

#### 2.10.1 Mini Module

There are two height options defined in the COM Express specification: 5mm and 8mm.

The height option is defined by the connectors on the baseboard.

The modules with Atom<sup>TM</sup> APL-I CPUs are equipped with an integrated heat spreader. This heat spreader adds 1.00 mm to CPU height against modules with CPUs without integrated heat spreader. This has no effect to the z-height of a module with mounted spreader.

### 2.11 Thermal Specifications

The cooling solution of a COM Express module is based on a heatspreader concept.

A heat-spreader is a metal plate (typically aluminum) mounted on the top of the module. The connection between this plate and the module components is typically done by thermal interface materials like phase change foils, gap pads and copper or aluminum blocks. A very good thermal conductivity is required in order to conduct the heat from the CPU and the chipset to the heat-spreader plate.

The heat-spreader of the MSC module is thermally attached using phase change materials and small aluminum blocks filling the gap between CPU and chipset dies and the heat-spreader plate.

**The heat-spreader is not a heat-sink!** It is a defined thermal interface for the system designer with fixed mechanical dimensions, so it should be possible to interchange different module types without problems. There must be a cooling solution for the system. The surface temperature of the heat-spreader should not exceed 80°C.

Main issue for the thermal functionality of a system is that each device of the module is operated within its specified thermal values. The max value for the SOC is 105°C (T die). So there may be system implementations where the heat-spreader temperature could be higher.

Anyway, in this case it has to be validated that there are no thermal specification violations of any assembled part or integrated circuit over the system temperature range even at worst case conditions.

Environment:

Ambient Temperature:

0°C … 60°C (operating) -40°C … +85°C (operating, extended temp.) -25°C … +85°C (storage)

Humidity: 5 ... 95% (operating, non-condensing) 5 ... 95% (storage, non-condensing)

Additionally MSC offers adequate heat-sink solutions for the different COM Express modules depending on the power dissipation of the implemented CPU. For more information please refer to <u>www.msc-technologies.eu</u> or contact your sales representative.

### 2.12 Use Conditions

The Use Conditions define run-time parameters such as the operating mode (eg. 24/7), activity factor, max frequency, temperature range etc. for the target application.

Certain Use Conditions may have an effect on the lifetime of the product.

For industrial use cases where longer lifetime and higher activity factors may be required, processor manufacturers may recommend to limit the performance of the processing units.

For such purposes MSC provides a special BIOS version for extended reliability. This BIOS is available for download from our support website.

Please consult the relevant processor manufacturer datasheets for more information.

### 2.13 Signal Description

Pins are marked in the following tables with the power rail associated with the pin, and, for input and I/O pins, with the input voltage tolerance. The pin power rail and the pin input voltage tolerance **may** be different. For example, the PCI group is defined as having a 3.3V power rail, meaning that the output signals will only be driven to 3.3V, but the pins are tolerant of 5V signals.

An additional label, "Sus", indicates that the pin is active during suspend states (S3, S4, S5). If suspend modes are used, then care must be taken to avoid loading signals that are active during suspend to avoid excessive suspend mode current draw.

Pin-Types:

I = Input.

O = Output.

- OD = Open Drain output.

- I/OD = Bi-directional Input/Open Drain Output Pin.

- I/O = Bi-directional Input/Output.

- ePU = external pull-up resistor on COM Express module.

- ePD = external pull-down resistor on COM Express module.

- eSR = external series resistor on COM Express module.

iPU = integrated pull-up resistor inside PCH or other IC, real value may vary from nominal one.

iPD = integrated pull-down resistor inside PCH or other IC, real value may vary from nominal one.

### 2.13.1 High Definition Audio

| Signal     |   | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR     | Description                                                      | Source / Target |

|------------|---|-----------------|---------------|-----------------------|--------------|------------------------------------------------------------------|-----------------|

| HDA_RST#   | 0 | CMOS            | 3.3V Sus      |                       | eSR = 33 Ω   | Reset output to CODEC, active low.                               | AL SOC          |

| HDA_SYNC   | 0 | CMOS            | 3.3V Sus      |                       | eSR = 33 Ω   | 48kHz fixed-rate, sample-synchronization signal to the CODEC(s), | AL SOC          |

| HDA_BITCLK | 0 | CMOS            | 3.3V Sus      |                       | eSR = 33 Ω   | 24.00 MHz serial data clock generated by the FCH                 | AL SOC          |

| HDA_SDOUT  | 0 | CMOS            | 3.3V Sus      |                       | eSR = 33 Ω   | Serial TDM data output to the CODEC, functional strap option     | AL SOC          |

| HDA_SDIN0  | I | CMOS            | 3.3V Sus      | 3.3V                  | ePD = 100 KΩ | Serial TDM data inputs from up to 3 CODECs.                      | AL SOC          |

### 2.13.2 Ethernet

| Signal                           | Pin<br>Type |        | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR                                                                 | Description                                                                                                                                                                                                                                  | Source /<br>Target    |

|----------------------------------|-------------|--------|---------------|-----------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| GBE0_MDI[0:3]+<br>GBE0_MDI[0:3]- | I/O         | Analog | 3.3V Sus      | 3.3V                  |                                                                          | Gigabit Ethernet Controller 0: Media Dependent Interface Differential<br>Pairs 0,1,2,3. The MDI can operate in 1000, 100 and 10 Mbit / sec<br>modes.<br>MDI[0]+/- B1_DA+/-<br>MDI[1]+/- B1_DB+/-<br>MDI[2]+/- B1_DC+/-<br>MDI[3]+/- B1_DD+/- | Intel® I210-<br>AT/IT |

| GBE0_ACT#                        | OD          | CMOS   | 3.3V Sus      | 5V / 20 mA            |                                                                          | Gigabit Ethernet Controller 0 activity indicator, active low.                                                                                                                                                                                | Intel® I210-AT/IT     |

| GBE0_LINK#                       | OD          | CMOS   | 3.3V Sus      | 5V / 20 mA            |                                                                          | Gigabit Ethernet Controller 0 link indicator, active low.                                                                                                                                                                                    | Intel® I210-AT/IT     |

| GBE0_LINK100#                    | OD          | CMOS   | 3.3V Sus      | 5V / 20 mA            | Gigabit Ethernet Controller 0 100 Mbit / sec link indicator, active low. |                                                                                                                                                                                                                                              | Intel® I210-<br>AT/IT |

| GBE0_LINK1000#                   | OD          | CMOS   | 3.3V Sus      | 5V / 20 mA            |                                                                          | Gigabit Ethernet Controller 0 1000 Mbit / sec link indicator, active low.                                                                                                                                                                    | Intel® I210-<br>AT/IT |

| GBE0_CTREF                       | REF         |        |               |                       |                                                                          | N/A. Center tab voltage not needed by Intel® I210-AT/IT.                                                                                                                                                                                     |                       |

#### 2.13.3 Serial ATA

| Signal                 |    | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR | Description                                     | Source / Target |

|------------------------|----|-----------------|---------------|-----------------------|----------|-------------------------------------------------|-----------------|

| SATA0_TX+<br>SATA0_TX- | 0  | SATA            | 1.24V         | AC coupled on module  |          | Serial ATA Channel 0 transmit differential pair | AL SOC          |

| SATA0_RX+<br>SATA0_RX- | I  | SATA            | 1.24V         | AC coupled on module  |          | Serial ATA Channel 0 receive differential pair  | AL SOC          |

| SATA1_TX+<br>SATA1_TX- | 0  | SATA            | 1.24V         | AC coupled on module  |          | Serial ATA Channel 1 transmit differential pair | AL SOC          |

| SATA1_RX+<br>SATA1_RX- | I  | SATA            | 1.24V         | AC coupled on module  |          | Serial ATA Channel 1 receive differential pair  | AL SOC          |

| ATA_ACT#               | OD | CMOS            | 3.3V          | 5V / 4mA              |          | SATA activity indicator, active low             | AL SOC          |

#### 2.13.4 PCI Express Lanes

| Signal                         | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR | Description                                                                             | Source / Target |

|--------------------------------|-------------|-----------------|---------------|-----------------------|----------|-----------------------------------------------------------------------------------------|-----------------|

| PCIE_TX[0:3]+<br>PCIE_TX[0:3]- | 0           | PCle            | 1.24V         | AC coupled on module  |          | PCI Express Differential Transmit Pairs 0 through 3                                     | AL SOC          |

| PCIE_RX[0:3]+<br>PCIE_RX[0:3]- | I           | PCle            | 1.24V         | AC coupled off module |          | PCI Express Differential Receive Pairs 0 through 3                                      | AL SOC          |

| PCIE_CLK_REF+<br>PCIE_CLK_REF- | 0           | PCle<br>CLK     | 1.05V         |                       |          | Differential Reference Clock output for all PCI Express and PCI Express Graphics lanes. | AL SOC          |

① NOTICE: Considerable care must be taken when using high speed signals on the carrier board. Reliable functionality depends on the following factors:

a. Trace length on the carrier board

b. Number of vias used on the carrier board

c. PCB material and specification used for the carrier board

d. Target device

### 2.13.5 Express Card Support

| Signal        |   | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD       | Description                          | Source / Target |

|---------------|---|-----------------|---------------|-----------------------|-------------|--------------------------------------|-----------------|

| EXCD[0]_CPPE# | I | CMOS            | 3.3V          | 3.3V                  | ePU = 10 KΩ | ExpressCard card request, active low | AL SOC          |

| EXCD[1]_CPPE# | I | CMOS            | 3.3V          | 3.3V                  | ePU = 10 KΩ | ExpressCard card request, active low | AL SOC          |

| EXCD[0]_RST#  | 0 | CMOS            | 3.3V          | 3.3V                  | ePU = 10 KΩ | ExpressCard reset, active low        | AL SOC          |

| EXCD[1]_RST#  | 0 | CMOS            | 3.3V          | 3.3V                  | ePU = 10 KΩ | ExpressCard reset, active low        | AL SOC          |

# **INDET** EMBEDDED

#### 2.13.6 USB

Attention: For USB Overcurrent Detection specifics, see Note 1 on next page!

| Signal                           | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR                  | Description                                                                                                                                                                                                                                      | Source /<br>Target |

|----------------------------------|-------------|-----------------|---------------|-----------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| USB[0:7]+<br>USB[0:7]-           | I/O         | USB             | 3.3V Sus      | 3.3V                  | iPD = 15 KΩ<br>iSR = 45 Ω | USB differential pairs, channels 0 through 7                                                                                                                                                                                                     | AL SOC             |

| USB_HOST_PRSNT                   | I           | CMOS            | 3.3V Sus      | 3.3V                  | ePD = 100 KΩ              | A high value indicates that a host is present at USB7 port.                                                                                                                                                                                      | AL SOC             |

| USB_0_1_OC#                      | I           | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 10 KΩ               | USB over-current sense, USB channels 0 and 1.<br>Pull-up is present on the module - do NOT pull this line high on<br>the Carrier Board! Pull this line LOW only by an Open-Drain<br>driver on the Carrier Board.<br>ATTENTION: SEE NOTE 1 BELOW! | AL SOC             |

| USB_2_3_OC#                      | I           | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 10 KΩ               | USB over-current sense, USB channels 2 and 3.<br>Pull-up is present on the module - do NOT pull this line high on<br>the Carrier Board! Pull this line LOW only by an Open-Drain<br>driver on the Carrier Board.<br>ATTENTION: SEE NOTE 1 BELOW! | AL SOC             |

| USB_4_5_OC#                      | I           | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 10 KΩ               | USB over-current sense, USB channels 4 and 5.<br>Pull-up is present on the module - do NOT pull this line high on<br>the Carrier Board! Pull this line LOW only by an Open-Drain<br>driver on the Carrier Board.<br>ATTENTION: SEE NOTE 1 BELOW! | AL SOC             |

| USB_6_7_OC#                      | I           | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 10 KΩ               | USB over-current sense, USB channels 6 and 7.<br>Pull-up is present on the module - do NOT pull this line high on<br>the Carrier Board! Pull this line LOW only by an Open-Drain<br>driver on the Carrier Board.<br>ATTENTION: SEE NOTE 1 BELOW! | AL SOC             |

| USB_SSTX[0:1]+<br>USB_SSTX[0:1]- | 0           | USB<br>3.0      | 1.24V<br>Sus  | AC coupled on module  |                           | USB 3.0 Differential Transmit Pairs 0 through 1                                                                                                                                                                                                  | AL SOC             |

| USB_SSRX[0:1]+<br>USB_SSRX[0:1]- | I           | USB<br>3.0      | 1.24V<br>Sus  | AC coupled off module |                           | USB 3.0 Differential Receive Pairs 0 through 1                                                                                                                                                                                                   | AL SOC             |

#### NOTE 1:

The Apollo Lake chipset offers only 2 Overcurrent Detection lines in total. Thus the 4 lines that the COM Express standard offers need to be combined logically into these only two Overcurrent signals.

- USB\_0\_1\_OC# and USB\_2\_3\_OC# are electrically separate (not just shorted together), but logically OR'ed together.

- USB\_4\_5\_OC# and USB\_6\_7\_OC# are electrically separate (not just shorted together), but logically OR'ed together.

If an Overcurrent condition occurs on **either one** of USB0, USB1, USB2 or USB3, **all of USB0...USB3** will be deactivated simultaneously. If an Overcurrent condition occurs on **either one** of USB4, USB5, USB6 or USB7, **all of USB4...USB7** will be deactivated simultaneously. As stated above, this limitation is forced by the chipset and cannot be changed.

(i) NOTICE: Considerable care must be taken when using high speed signals on the carrier board. Reliable functionality depends on the following factors:

- a. Trace length on the carrier board

- b. Number of vias used on the carrier board

- c. PCB material and specification used for the carrier board

- d. Target device

### 2.13.7 LPC Bus

| Signal      |      | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR    | Description                                               | Source / Target |

|-------------|------|-----------------|---------------|-----------------------|-------------|-----------------------------------------------------------|-----------------|

| LPC_AD[0:3] | I/O  | CMOS            | 3.3V          | 3.3V                  |             | LPC multiplexed address, command and data bus             | AL SOC          |

| LPC_FRAME#  | 0    | CMOS            | 3.3V          |                       |             | LPC frame indicates the start of an LPC cycle             | AL SOC          |

| LPC_DRQ0#   |      | CMOS            | 3.3V          | 3.3V                  |             | LPC serial DMA request not available                      | AL SOC          |

| LPC_DRQ1#   |      | CMOS            | 3.3V          |                       |             | LPC serial DMA request not available                      | AL SOC          |

| LPC_SERIRQ  | I/OD | CMOS            | 3.3V          | 3.3V                  | ePU = 10 KΩ | LPC serial interrupt                                      | AL SOC          |

| LPC_CLK     | 0    | CMOS            | 3.3V          |                       | eSR = 10 Ω  | LPC clock output - 33MHz nominal, functional strap option | AL SOC          |

### 2.13.8 LVDS / eDP

| Signal Name LVDS | Pin Number | Signal Name eDP (Option) |

|------------------|------------|--------------------------|

| LVDS_A0+         | A71        | eDP_TX2+                 |

| LVDS_A0-         | A72        | eDP_TX2-                 |

| LVDS_A1+         | A73        | eDP_TX1+                 |

| LVDS_A1-         | A74        | eDP_TX1-                 |

| LVDS_A2+         | A75        | eDP_TX0+                 |

| LVDS_A2-         | A76        | eDP_TX0-                 |

| LVDS_A_CK+       | A81        | eDP_TX3+                 |

| LVDS_A_CK-       | A82        | eDP_TX3-                 |

| LVDS_VDD_EN      | A77        | eDP_VDD_EN               |

| LVDS_BKLT_EN     | B79        | eDP_BKLT_EN              |

| LVDS_BKLT_CTRL   | B83        | eDP_BKLT_CTRL            |

| LVDS_I2C_CK      | A83        | eDP_AUX+                 |

| LVDS_I2C_DAT     | A84        | eDP_AUX-                 |

| RSVD             | A87        | eDP_HPD                  |

| Signal                       |      | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR     | Description                             | Source / Target        |

|------------------------------|------|-----------------|---------------|-----------------------|--------------|-----------------------------------------|------------------------|

| LVDS_A[0:3]+<br>LVDS_A[0:3]- | 0    | LVDS            |               |                       |              | LVDS Channel A differential pairs       | ANX1122                |

| LVDS_A_CK+<br>LVDS_A_CK-     | 0    | LVDS            |               |                       |              | LVDS Channel A differential clock       | ANX1122                |

| LVDS_VDD_EN                  | 0    | CMOS            | 3.3V          |                       |              | LVDS panel power enable                 | ANX1122                |

| LVDS_BKLT_EN                 | 0    | CMOS            | 3.3V          |                       |              | LVDS panel backlight enable             | Embedded<br>Controller |

| LVDS_BKLT_CTRL               | 0    | CMOS            | 3.3V          |                       |              | LVDS panel backlight brightness control | Embedded<br>Controller |

| LVDS_I2C_CK                  | 0    | CMOS            | 3.3V          |                       | ePU = 2.2 KΩ | I2C clock output for LVDS display use   | ANX1122                |

| LVDS_I2C_DAT                 | I/OD | CMOS            | 3.3V          | 3.3V                  | ePU = 2.2 KΩ | I2C data line for LVDS display use      | ANX1122                |

#### 2.13.8.1 LVDS Flat Panel (mounting option, only available on modules with LVDS mounting option)

| Signal                       | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance       | PU/PD/SR     | Description                                                       | Source / Target        |

|------------------------------|-------------|-----------------|---------------|-----------------------------|--------------|-------------------------------------------------------------------|------------------------|

| eDP_TX[0:3]+<br>eDP_TX[0:3]- | 0           | PCle            |               | AC coupled off module       |              | eDP differential pairs                                            | AL SOC                 |

| eDP_VDD_EN                   | 0           | CMOS            | 3.3V          | 3.3V                        |              | eDP power enable                                                  | AL SOC                 |

| eDP_BKLT_EN                  | 0           | CMOS            | 3.3V          | 3.3V                        |              | eDP backlight enable                                              | Embedded<br>Controller |

| eDP_BKLT_CTRL                | 0           | CMOS            | 3.3V          | 3.3V                        |              | eDP backlight brightness control                                  | Embedded<br>Controller |

| eDP_AUX+                     | I/O         | PCle            |               | AC<br>coupled off<br>module |              | eDP_AUX+                                                          | AL SOC                 |

| eDP_AUX-                     | I/O         | PCle            |               | AC<br>coupled off<br>module |              | eDP_AUX-                                                          | AL SOC                 |

| eDP_HPD                      | 1           | CMOS            | 3.3V          | 3.3V                        | ePD = 100 KΩ | Detection of Hot Plug / Unplug and notification of the link layer | AL SOC                 |

#### 2.13.8.2 eDP (mounting option, only available on modules with eDP mounting option)

#### 2.13.9 Digital Display Interfaces

#### 2.13.9.1 Overview Type10 DDI Video Type Mapping

|      | Signal                   | DP           | HDMI/DVI (TMDS Signaling) |

|------|--------------------------|--------------|---------------------------|

|      | DDI0_PAIR0+/-            | DP0_LANE0+/- | TMDS0_DATA2+/-            |

|      | DDI0_PAIR1+/-            | DP0_LANE1+/- | TMDS0_DATA1+/-            |

|      | DDI0_PAIR2+/-            | DP0_LANE2+/- | TMDS0_DATA0+/-            |

| DDI0 | DDI0_PAIR3+/-            | DP0_LANE3+/- | TMDS0_DATACLK+/-          |

|      | DDI0_HPD                 | DP0_HPD      | HDMI0_HPD                 |

|      | DDI0_CTRLCLK/DATA_AUX+/- | DP0_AUX+/-   | HDMI0_CTRLCLK/DATA        |

|      | DDI0_DDC_AUX_SEL         |              |                           |

#### 2.13.9.2 DisplayPort

| Signal                           |     | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR                     | Description                                                                                                                                            | Source / Target                |

|----------------------------------|-----|-----------------|---------------|-----------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| DP0_LANE[0:3]+<br>DP0_LANE[0:3]- | 0   |                 |               | AC coupled off module |                              | DisplayPort Lane [0:3] differential pairs.                                                                                                             | AL SOC                         |

| DP0_AUX+<br>DP0_AUX-             | I/O |                 |               | AC coupled on module  | ePD = 100 KΩ<br>ePU = 100 KΩ | DisplayPort Aux control channel differential pair                                                                                                      | AL SOC                         |

| DP0_HPD                          | I   | CMOS            | 3.3V          | 3.3V                  | ePD = 100 KΩ                 | DisplayPort Hot Plug Detect.                                                                                                                           | AL SOC                         |

| DDI0_DDC_AUX_SEL                 | I   | CMOS            | 3.3V          | 3.3V                  | ePD = 1 MΩ                   | If this input is floating the AUX pair is used for the DP AUX+/-<br>signals. If pulled high the AUX pair contains the CTRLCLK and<br>CTRLDATA signals. | Carrier board<br>logic circuit |

#### 2.13.9.3 HDMI / DVI

| Signal                               | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR     | Description                                                                                           | Source / Target             |

|--------------------------------------|-------------|-----------------|---------------|-----------------------|--------------|-------------------------------------------------------------------------------------------------------|-----------------------------|

| TMDS0_DATA[0:2]+<br>TMDS0_DATA[0:2]- | 0           | TMDS            |               | AC coupled off module |              | HDMI/DVI TMDS Data [0:2] output differential pairs.                                                   | AL SOC                      |

| TMDS0_DATACLK+<br>TMDS0_DATACLK-     | 0           | TMDS            |               | AC coupled off module |              | HDMI/DVI TMDS Clock differential pairs.                                                               | AL SOC                      |

| HDMI0_CTRLCLK                        | I/O         | CMOS            | 3.3V          | 3.3V                  | ePD = 100 KΩ | HDMI/DVI Control Clock. Shared with DP1_AUX+.                                                         | AL SOC                      |

| HDMI0_CTRLDATA                       | I/O         | CMOS            | 3.3V          | 3.3V                  | ePU = 100 KΩ | HDMI/DVI Control Data. Shared with DP1_AUX                                                            | AL SOC                      |

| HDMI0_HPD                            | I           | CMOS            | 3.3V          | 3.3V                  | ePD = 100 KΩ | HDMI/DVI Hot Plug Detect.                                                                             | AL SOC                      |

| DDI0_DDC_AUX_SEL                     | I           | CMOS            | 3.3V          | 3.3V                  | ePD = 1 MΩ   | Pull to 3.3V on the Carrier with 100k Ohm resistor to configure the DDI1_AUX pair as the DDC channel. | Carrier board logic circuit |

#### 2.13.10 Serial Interface Signals

| Signal  |   | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR    | Description                                      | Source /<br>Target |

|---------|---|-----------------|---------------|-----------------------|-------------|--------------------------------------------------|--------------------|

| SER0_TX | 0 | CMOS            | 3.3V          | 12V, 7mA              |             | General purpose serial port transmitter (output) | AL SOC             |

| SER0_RX | I | CMOS            | 3.3V          | 12V                   | ePU = 47 KΩ | General purpose serial port receiver (input)     | AL SOC             |

| SER1_TX | 0 | CMOS            | 3.3V          | 12V, 7mA              |             | General purpose serial port transmitter (output) | AL SOC             |

| SER1_RX | I | CMOS            | 3.3V          | 12V                   | ePU = 47 KΩ | General purpose serial port receiver (input)     | AL SOC             |

#### 2.13.11 Miscellaneous

| Signal       |     | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR         | Description                                                                                  | Source / Target             |

|--------------|-----|-----------------|---------------|-----------------------|------------------|----------------------------------------------------------------------------------------------|-----------------------------|

| I2C_CK       | I/O | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 2.2 KΩ     | General purpose I2C port clock output                                                        | AL SOC                      |

| I2C_DAT      | I/O | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 2.2 KΩ     | General purpose I2C port data I/O line                                                       | AL SOC                      |

| SPKR         | 0   | CMOS            | 3.3V          | 3.3V, 7mA             |                  | Output for audio enunciator - the "speaker" in PC-AT systems                                 | AL SOC                      |

| BIOS_DIS[1]# | I   | CMOS            | 3.3V          |                       | ePU = 10 KΩ      | Module BIOS disable input                                                                    | Carrier board logic circuit |

| BIOS_DIS[0]# | I   | CMOS            | 3.3V          |                       | ePU = 10 KΩ      | Module BIOS disable input, not connected                                                     | Carrier board logic circuit |

| WDT          | 0   | CMOS            | 3.3V          |                       | ePD = 10 KΩ      | Active high output indicating that a watchdog time-out has occurred.                         | Embedded<br>Controller      |

| FAN_PWMOUT   | 0   | CMOS            | 3.3V          |                       |                  | Fan speed control. Uses the Pulse Width Modulation (PWM) technique to control the fan's RPM. | Embedded<br>Controller      |

| FAN_TACHIN   | I   | CMOS            | 3.3V          |                       | ePU = 10 KΩ      | Fan tachometer input for a fan with a two pulse output.                                      | Embedded<br>Controller      |

| TPM_PP       | I   | CMOS            | 3.3V          | 3.3V                  | ePD = 4.99<br>KΩ | Trusted Platform Module (TPM) Physical Presence pin. Active high.                            | ТРМ                         |

(i) NOTICE: COM Express Specification R2.1 redefines the I2C bus to be in the suspend plane 3.3V\_SUS rather than in the 3.3V plane.

### 2.13.12 Power and System Management

| Signal     | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR    | Description                                                                                                                                                                                                                                                                       | Source / Target                   |

|------------|-------------|-----------------|---------------|-----------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| PWRBTN#    | I           | CMOS            | 3.3V Sus      |                       | ePU = 10 KΩ | Power button to bring system out of or into Suspend states.                                                                                                                                                                                                                       | Embedded<br>Controller            |

| SYS_RESET# | I           | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 10 KΩ | Reset button input.                                                                                                                                                                                                                                                               | Embedded<br>Controller            |

| CB_RESET#  | 0           | CMOS            | 3.3V Sus      | 3.3V, 7mA             |             | Reset output from module to Carrier Board. Active low. Issued by module chipset and may result from a low SYS_RESET# input, a low PWR_OK input, a VCC_12V power input that falls below the minimum specification, a watchdog timeout, or may be initiated by the module software. | AL SOC                            |

| PWR_OK     | I           | CMOS            | 3.3V Sus      | 12V                   | ePU = 47 KΩ | Power OK from main power supply. A high value indicates that the power is good.                                                                                                                                                                                                   | Power logic<br>circuit            |

| SUS_STAT#  | 0           | CMOS            | 3.3V Sus      | 3.3V                  |             | Indicates imminent suspend operation; used to notify LPC devices.                                                                                                                                                                                                                 | AL SOC                            |

| SUS_S3#    | 0           | CMOS            | 3.3V Sus      | 3.3V,<br>24mA         |             | Indicates system is in Suspend to RAM state. Active low output.                                                                                                                                                                                                                   | AL SOC                            |

| SUS_S4#    | 0           | CMOS            | 3.3V Sus      | 3.3V,<br>24mA         |             | Indicates system is in Suspend to Disk state. Active low output.<br>Shorted to SUS_S5#.                                                                                                                                                                                           | AL SOC                            |

| SUS_S5#    | 0           | CMOS            | 3.3V Sus      | 3.3V,<br>24mA         |             | Indicates system is in Soft Off state. Also known as "PS_ON" and can be used to control an ATX power supply.                                                                                                                                                                      | AL SOC                            |

| WAKE0#     | Ι           | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 10 KΩ | PCI Express wake-up signal.                                                                                                                                                                                                                                                       | AL SOC                            |

| WAKE1#     | I           | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 10 KΩ | General purpose wake up signal. May be used to implement wake-<br>up on PS2 keyboard or mouse activity.                                                                                                                                                                           | AL SOC                            |

| BATLOW#    | I           | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 10 KΩ | Indicates that external battery is low.                                                                                                                                                                                                                                           | AL SOC,<br>Embedded<br>Controller |

| LID#       | 1           | CMOS            | 3.3V Sus      | 12V                   | ePU = 10 KΩ | LID switch. Low active signal used by ACPI operating system for LID switch.                                                                                                                                                                                                       | AL SOC,<br>Embedded<br>Controller |

| Signal     | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR     | Description                                                                                                                                                               | Source / Target                   |

|------------|-------------|-----------------|---------------|-----------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| SLEEP#     | I           | CMOS            | 3.3V Sus      | 12V                   | ePU = 10 KΩ  | Sleep button. Low active signal used by ACPI operating system to bring the system to sleep state or wake it up again.                                                     | AL SOC,<br>Embedded<br>Controller |

| THRM#      |             | CMOS            | 3.3V          | 3.3V                  | ePU = 10 KΩ  | Input from off-module temperature sensor indicating an over-temp situation. Not supported.                                                                                | AL SOC,<br>Embedded<br>Controller |

| THRMTRIP#  | 0           | CMOS            | 3.3V          | 3.3V,<br>24mA         | ePU = 10 KΩ  | Active low output indicating that the CPU has entered thermal shutdown.                                                                                                   | AL SOC,<br>Embedded<br>Controller |

| SMB_CK     | I/O<br>OD   | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 2.2 KΩ | System Management Bus bidirectional clock line. Power sourced through 3.3V standby rail.                                                                                  | AL SOC,<br>Embedded<br>Controller |

| SMB_DAT    | I/O<br>OD   | CMOS            | 3.3V Sus      | 3.3V                  | ePU = 2.2 KΩ | System Management Bus bidirectional data line. Power sourced through 3.3V standby rail.                                                                                   | AL SOC,<br>Embedded<br>Controller |

| SMB_ALERT# | I           | CMOS            | 3.3V Sus      | 3.3V                  | ePU =2.2 KΩ  | System Management Bus Alert – active low input can be used to generate SMI# (System Management Interrupt) or to wake the system. Power sourced through 3.3V standby rail. | AL SOC,<br>Embedded<br>Controller |

### 2.13.13 General Purpose I/O

| Signal   |   | Signal<br>Level | Power<br>Rail | Remark /<br>Tolerance | PU/PD/SR | Description                                                                                                                   | Source / Target |

|----------|---|-----------------|---------------|-----------------------|----------|-------------------------------------------------------------------------------------------------------------------------------|-----------------|

| GPI[0:3] | I | CMOS            | 3.3V          | 3.3V                  |          | General purpose input pins. Pulled high internally on the module. These signals are multiplexed with SDIO interface.          | AL SOC          |